PCI加密芯片

PCI加密芯片

高性能PCI/PCI-E接口加解密芯片,是款通用的密码运算协处理器,内嵌高性能硬件密码运算模块,能够利用总线的该芯片是款突发模式实现大数据块的加解密运算。由于采用了通用的PCI/PCI-E的局部总线接口,可以方便地嵌入到各种形式的计算机系统中,如PC机、笔记本、各种服务器和各种掌上电子设备等。

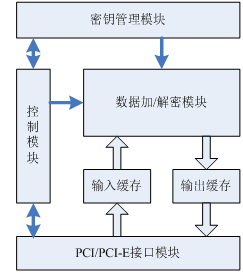

芯片微体系结构如图1所示:

图1 芯片微体系结构图

内部逻辑模块主要由:A)数据加解密模块;B)密钥管理模块;C)控制模块;D)总线接口模块组成。

数据通道有:

A)主机通过PCI/PCI-E接口,将要加/解密的数据置入输入缓存中,数据加/解密模块在控制模块的控制下完成加/解密运算,并将运算好的数据置入输出缓存中,PCI/PCI-E接口模块最终将数据返回到主机内存中;

B)主机通过PCI/PCI-E接口向控制模块发出指令,控制或读取当前加/解密模块和密钥管理模块的运行与状态;

C)密钥管理模块与芯片外部USB接口型或智能卡型密钥的密钥载体相互配合,进行密钥的管理,负责数据加/解密模块所用密钥的生成、验证、存储和撤销等。

特点

² 采用可综合、可复用的Verilog-HDL语言设计,方便做成专用集成电路;

² 采用单时钟同步的逻辑设计,芯片制成简单、成本低;

² PCI总线接口遵循规范2.2,总线数据宽度为32位,时钟频率为66MHz,单功能,可工作在主/从

方式;

² PCI-E总线接口遵循规范2.0,采用4X的接口模式;

² 为了保证总线之间的高速数据传输,采用大容量的双口同步SRAM作为FIFO;

² 内嵌高性能硬加/解密运算模块,支持如SM4、DES、TDES和AES等对称加密算法;

² 也可以内嵌或外挂,公开密钥算法(如SM2、RSA和ECC等)模块或特定国内算法;

² 内嵌8051微控制器,用于对智能卡密钥的管理;

² 利用PCI ROM程序,实现用户口令的认证,实现开机要有密钥和口令;

² 只有通过用户口令的验证,解密处理器才能加载密钥,机器才能启动;

² 含有XOR Flash控制接口,可以实现ROM的位置;

² 适用于台式机、服务器、笔记本和各种移动计算通信设备等。